Cortex-M7 Launches: Embedded, IoT and Wearables

by Stephen Barrett on September 23, 2014 7:01 PM EST

Introduction

Last week, I had the distinct pleasure of visiting ARM’s Austin Texas campus for a meeting with Vice President of CPU Product Marketing Nandan Nayampally. The topic of discussion: ARM’s next Cortex-M processor, codename Pelican, is officially launching today as the Cortex-M7. Thankfully, unlike the A series CPU cores mobile device enthusiasts have grown to love, M and R series cores are typically announced at the same time as retail availability from ARM’s customers. ARM has therefore been working with lead semiconductor partners for some time, and their fully integrated products should have similar launch announcements soon.

If you are not familiar with the M and R series processors from ARM, I don’t blame you. These microcontroller processors don’t receive quite the coverage as A series application processors like the A7, A9, A15, A53 and A57 do. Considering my own heritage learning about PC technology, this is understandable. I always wanted to learn about the latest processors from AMD and Intel as these most directly related to my productivity and entertainment. However, if the smartphone wave was any indication, the next decade of productivity and entertainment might come from processors we don’t expect or even know about.

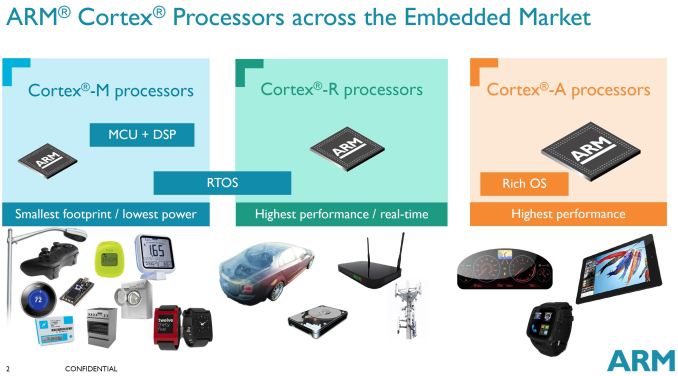

Fundamentally, the M series processors are considered microcontrollers and not application processors, mainly because they lack a memory management unit (MMU). An MMU’s primary role is to sit between the processor and memory, intercepting all memory references and performing translation between virtual addresses and physical addresses. General purpose operating systems such as Linux (Android), Windows, OSX, and iOS require an MMU to function. That means M series processors, like all microcontrollers (MCUs), will never be tasked with running general purpose operating systems.

MCU proliferation is actually already happening today. Nandan mentioned that a device containing a single R or A series processor might also contain dozens of Cortex-M processors performing a variety of tasks that make your life better. Nandan couldn’t mention any specific implementations, as he deferred to ARM's customer’s for that, but everything from smart thermostats, simple smart watches like the Pebble, and IC power management units are implemented with low power microcontrollers.

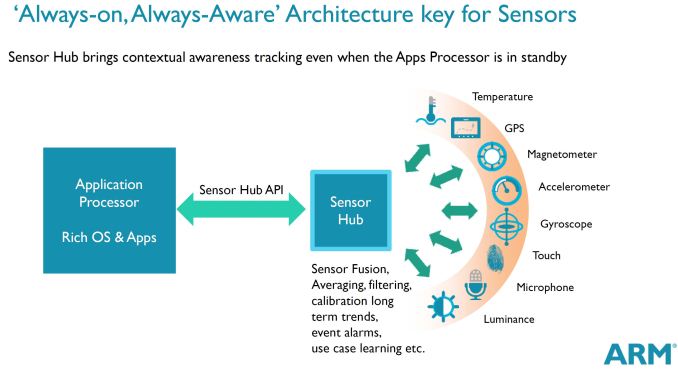

Even features we love on our high powered smartphones such as Microsoft’s Lumia Glance Screen and SensorCore, Motorola’s Moto Voice and Moto Display, and the iPhone’s Motion Coprocessor cannot be directly attributed to bigger faster application processors but rather come from MCUs, and arguably they have just as big an impact on our lives as a lower Sunspider score.

Looking at ARM’s track record in the past five years, one can easily correlate their success with the smartphone craze started with the original iPhone containing an ARM11 processor. From there, the 3GS upgraded to a Cortex-A8, 4S used the Cortex-A9, and Google attacked the same market with Android supporting the ARM11 and subsequent ARM cores as well. While ARM’s meteoric rise might have started with the ARM11, it was years of prior work that provided a solid foundation for partners and customers. In fact there were 11 cores released prior to the ARM11 (fancy that), including six revisions to their instruction set.

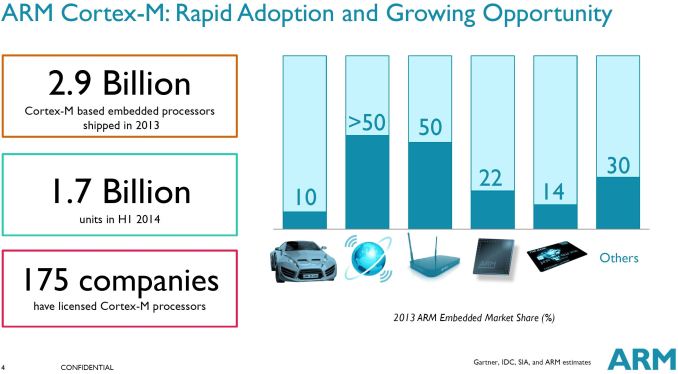

ARM has been investing in the Cortex-M line since 2004, when they first released the Cortex-M3. For a decade, ARM has been combating 8-bit and 16-bit microcontrollers with their 32-bit M series. With the release of the M7, ARM feels they have a very complete microcontroller lineup and have effectively “crossed the chasm” into the mainstream. The competition continues today, but with eight billion (yes, with a b) processors shipped to date containing at least one Cortex-M core, the M series is higher volume than all other ARM cores combined. In the first half of this year alone, ARM’s partners have shipped 1.7 billion Cortex-M units, where a unit is defined as a chip containing at least one Cortex-M processor.

Responding to market demand for powerful voice, sensor, display, and control offloading, ARM brings a higher performance, feature rich core to the Cortex-M family with the M7.

43 Comments

View All Comments

Wilco1 - Wednesday, September 24, 2014 - link

Embedded (M) was traditionally a micro controller using on-chip flash and SRAM, no MMU, no DSP, no FP support. The R series are higher performance realtime CPUs with TCM, caches, branch prediction and often external DRAM and FP. Now that M also supports DSP, FP, caches, and is becoming high performance, things have become blurred. The ISA differences are now the main distinction, M only supports Thumb-1, Thumb-2 and uses a different interrupt model, while the R architecture is basically A series plus TCM minus MMU. So many TLA's...hammer256 - Wednesday, September 24, 2014 - link

Oh that's right, different interrupt model. M series is generally lower latency because it's directly coupled, if I recall. It's just that this new M7 line blurs that line even further than the M4 did...For TCM, is it generally DRAM integrated on the MCU, or a tight interface between the MCU and the DRAM chips?

Didn't one of samsung's SSDs use a few Cortex-R3 cores for their controller?

Wilco1 - Wednesday, September 24, 2014 - link

3 R4 cores are used in Samsung SSDs.Simply put, TCM is fast on-core instruction/data SRAM, similar to an I- or D-cache. It is fully under user control and thus without the non-deterministic effects of a traditional cache. TCM can be used in addition to a cache. TCM allows high frequencies like a cache, and thus is faster than an external SRAM.

The usage model is that you put all your critical realtime code/data in the instruction/data TCMs and run the rest from flash/DRAM. When an interrupt occurs, you start executing realtime code from the TCM immediately rather than having to wait for cache misses that inevitably occur if you didn't have TCM. So the TCMs are actually necessary for realtime on a fast CPU, having a low interrupt latency alone is not the whole story.

hammer256 - Wednesday, September 24, 2014 - link

Oooh I see. It sounds like TCM is a big distinguishing feature between the M and R series then. So even if performance is equal, R series actually allows for applications with even tighter latency requirements than the M series.Well, learned something new today, thanks!

toyotabedzrock - Wednesday, September 24, 2014 - link

It is not a good idea to put this in a wearable or a car. The lack of an MMU seems tone deaf given the security environment we live in.Wilco1 - Wednesday, September 24, 2014 - link

Most of the M series support an optional MPU for OS task protection. That said, security and MMU are 2 orthogonal things - an MMU doesn't stop exploits as otherwise we wouldn't have any viruses/trojans/rootkits/etc on PCs. For microcontrollers security is easier as there are far fewer possible security breaches, so it's more down to not setting default passwords or using old, already broken encryption algorithms.ah06 - Thursday, September 25, 2014 - link

Which one makes most sense in a wearable? M4, M7, Rx, A7, A53?Wilco1 - Thursday, September 25, 2014 - link

IMHO only M3 or M4 - anything else is way overkill for eg. a watch. You definitely don't want to run anything as big/complex as Linux/Android if you want to provide at least a week of battery life.DIYEyal - Sunday, September 28, 2014 - link

Actually the WeLoop tommy smartwatch has the M0, they claim 3 weeks of battery life with a 110mAh battery.RomanR - Thursday, September 25, 2014 - link

Hi,who can tell me: how many clock cycles will be needed for ten taps 32-bit FIR filter output sample computation ?

1 cycle MAC instruction is O.K. but what about data transfer ?