Intel to Create RISC-V Development Platform with SiFive P550 Cores on 7nm in 2022

by Dr. Ian Cutress on June 22, 2021 9:01 AM EST

As part of SiFive’s announcements today, along with enabling SiFive IP on Intel’s Foundry Service offerings, Intel will be creating its own RISC-V development platform using its 7nm process technology. This platform, called Horse Creek, will feature several of SiFive’s new Performance P550 cores also being announced today, and will be paired with Intel’s DDR and PCIe IP technology.

On first reading into the press release, it isn’t 100% clear that Intel’s commentary discusses a platform with P550 as a host or as an add-in device: to quote Intel, ‘We are pleased to be a lead development partner with SiFive to showcase to mutual customers the impressive performance of their P550 on our 7nm Horse Creek platform’. Intel historically typically keeps its Creek family names, such as Boulder Creek, Cherry Creek, or Timber Creek, for socketed platforms - not for all-in-one embedded development platforms. Not only that, the wording makes it sound like we should consider a RISC-V core as an assistant core managing another part of a system.

However it would appear that Intel intends to make this a fully-featured development system, along similar lines to SiFive’s own HiFive Unmatched platform launched early this year. What makes this special is that Intel is committing to developing the SoC on its own 7nm process node, which provides a ‘simpler’ vehicle for Intel to test and ramp up its 7nm technology. This can be coupled with increasing interest in RISC-V development, and deploying a platform though Intel’s supply chain and distribution might have a far reach to put these in the hands of upcoming developers.

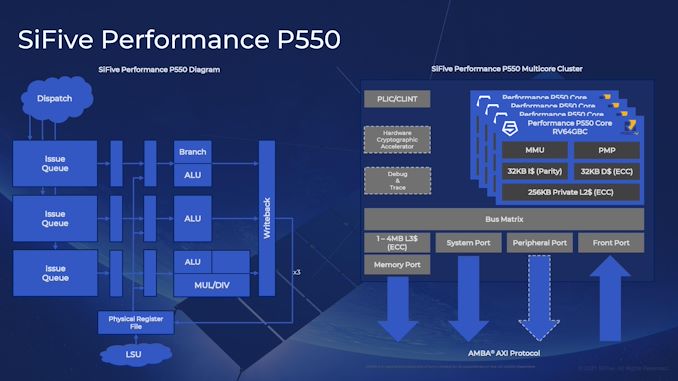

The new SiFive Performance P550 core at the heart of Horse Creek is SiFive’s highest performance processor to date, with the company quoting a SPEC2006int of 8.65 per GHz. It is a Linux-capable core, with full support for the RISC-V vector extension v1.0rc. It has a 13-stage triple-issue out-of-order microarchitecture with a private 32KB+32KB L1 cache and a private L2 cache (per core) The design supports four cores in a single cluster that can be paired up to 4 MB of shared L3.

The time scale for this platform coming to market is quite interesting. Despite Intel recently committed to bringing its 7nm to market in 2023 with the compute tile for its Meteor Lake processor as its first 7nm product, we’re being told that Horse Creek silicon will be ready in 2022, which would make Horse Creek its first 7nm product. For what it is worth, it’s unlikely that the Intel RISC-V solution is tile-based, but it might be easy enough to bring a small RISC-V chip development platform to market around then. The chip is likely to be small, so that might work in favor of its costs as well. A question does remain as to whether Intel’s involvement here is purely in the hardware, or whether there will be an Intel-based software stack to go along with it.

Related Reading

- Samsung to Use SiFive RISC-V Cores for SoCs, Automotive, 5G Applications

- SiFive Announces First RISC-V OoO CPU Core: The U8-Series Processor IP

- SiFive Acquires USB 2.0 and 3.x IP Portfolio to Strengthen RISC-V SoCs

- SiFive Unveils Freedom Platforms for RISC-V-Based Semi-Custom Chips

- Western Digital’s RISC-V "SweRV" Core Design Released For Free

35 Comments

View All Comments

SarahKerrigan - Tuesday, June 22, 2021 - link

Glad to see someone appreciating TileGX/TileMX.brucethemoose - Tuesday, June 22, 2021 - link

Thats's pretty much the exact opposite of what I was thinking though.I would propose stuffing as many 4-core dies one can cram into a giant package, and have them all hang off a EPYC style IO die built on a cheaper (22nm?) process.

Inter-cluster speeds would be anemic, but that doesn't really matter for a bunch of VMs partitioned to use 1 or 2 tiles each. And one wouldn't have to target some exotic VLIW ISA.

whatthe123 - Tuesday, June 22, 2021 - link

that sounds insanely inefficient. epyc is already memory/bandwidth starved, adding in a bunch of small clusters of cores running off that type of I/O is just going to cripple performance any time there are multiple users. may as well just buy epyc as its already over the limit of what that type of I/O system can handle without moving to more expensive fabric.MikeMurphy - Tuesday, June 22, 2021 - link

Intel sold XScale in 2006 to promote x86 reliance. As it turns out the world is no longer reliance on x86 and Intel again finds itself behind.MiauwMing - Wednesday, July 7, 2021 - link

Intel was the first one who tried to kill x86 with IA-64 architecture back in 2001. And Intel is currently producing 10nm ARM SOC for their FPGA products (since 2019).x86 is still going strong in Desktop/Laptop space. Soon it will also be the fastest (exascale) supercomputer with Aurora (1 exaflop, Intel), Frontier (1.5 exaflop, AMD) and El Capitan(2 exaflop, AMD). The arm based Japanese supercomputer is at 0.442 exaflop.

3arn0wl - Tuesday, June 22, 2021 - link

Intel might do well to spend some time developing a RISC-V translation layer for X Org apps, as Apple have done with Rosetta 2 for their M1 silicon.michael2k - Tuesday, June 22, 2021 - link

I'm not sure that makes any sense. Rosetta 2 is a translation from x86->ARMSo what you're proposing is an x86->RiscV translator?

That aside, why the focus on XOrg? XWindows isn't exactly the biggest player in Linux any more; Android dwarfs all the other Linux installs, and in that space you want ARM->RiscV!

3arn0wl - Tuesday, June 22, 2021 - link

Enterprise is Intel's bread and butter. IF they really are going down the RISC-V route in a serious way - and I think they should - then they're going to want to keep all their current customers. The reality is that users like the OSs and apps they know, and are slow to adapt... X86 -> RISC-V ensures that the apps people want are immediately available to them. ARM -> RISC-V doesn't.Of course, as with M1, native apps would run much quicker, and I'm sure that FOSS devs are keen to ensure that their software is running well on RISC-V.

mode_13h - Wednesday, June 23, 2021 - link

"X Org" must've been a case of getting the mental wires crossed? It only makes sense if 3arn0wl meant "x86".Wereweeb - Tuesday, June 22, 2021 - link

Welcome to the 21th century, Intel. Now, hands off SiFive please.